对于layout的工程师们来说,在PCB设计中如何提高电路板的抗干扰能力成为众多工程师们关注的重点问题之一。在这里,电路板厂家为您介绍电路板设计中降低噪声与电磁干扰的一些小窍门,千万不要错过哦~

(1)能用低速芯片就不用高速的,高速芯片用在关键地方。

(2)可用串一个电阻的办法,降低控制电路上下沿变速率。

(3)尽量为继电器等提供某种形式的阻尼。

(4)使用满足系统要求的最低频率时钟。

(5)时钟产生器尽量近到用该时钟的器件。石英晶体振荡器外壳要接地。

(6)用地线将时钟区圈起来,时钟线尽量短。

(7)I/O驱动电路尽量近印制电路板边,让其尽快离开印制电路板。对进入印制电路板的信号要加滤波,从高噪声区来的信号也要加滤波,同时用串终端电阻的办法,减小信号反射。

(8)MCD无用端要接高,或接地,或定义成输出端,集成电路上该接电源地的端都要接,不要悬空。

(9)闲置不用的门电路输入端不要悬空,闲置不用的运放正输入端接地,负输入端接输出端。

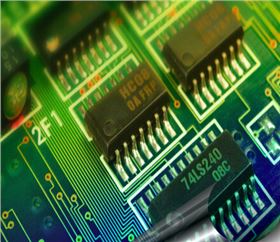

汽车BMS板

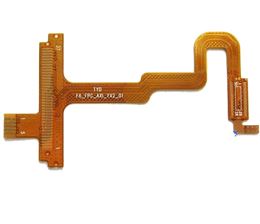

汽车BMS板 医疗设备FPC

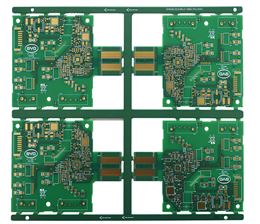

医疗设备FPC 通讯功放 PCB

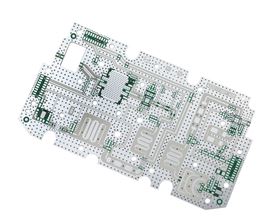

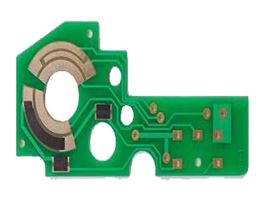

通讯功放 PCB 汽车传感器板PCB

汽车传感器板PCB