在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在PCB厂某些线路板设计中,高速差分过孔之间也会产生较大的串扰,PCB厂小编对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。

高速差分过孔间的串扰

对于板厚较厚的PCB来说,板厚有可能达到2.4mm或者3mm。以3mm的单板为例,此时一个通孔在PCB上Z方向的长度可以达到将近118mil。如果PCB上有0.8mm pitch的BGA的话,BGA器件的扇出过孔间距只有大约31.5mil。

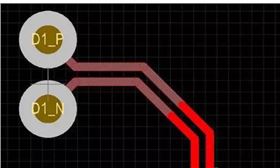

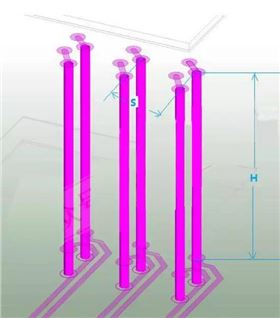

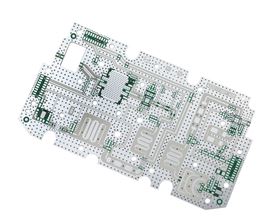

如图1所示,两对相邻差分过孔之间Z方向的并行长度H大于100mil,而两对差分过孔在水平方向的间距S=31.5mil。在过孔之间Z方向的并行距离远大于水平方向的间距时,就要考虑高速信号差分过孔之间的串扰问题。顺便提一下,高速PCB设计的时候应该尽可能最小化过孔stub的长度,以减少对信号的影响。如下图所1示,靠近Bottom层走线这样Stub会比较短。或者可以采用背钻的方式。

图1:高速差分过孔产生串扰的情况(H>100mil, S=31.5mil )

差分过孔间串扰的仿真分析

汽车BMS板

汽车BMS板 医疗设备FPC

医疗设备FPC 通讯功放 PCB

通讯功放 PCB 汽车传感器板PCB

汽车传感器板PCB