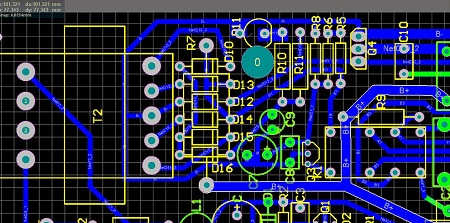

高速PCB印刷线路板信号完整性设计之布线技巧

在高速PCB印刷线路板的设计和制造过程中,工程师需要从布线、元件设置等方面入手,以确保这一PCB板具有良好的信号传输完整性。在今天的文章中,我们将会为各位新人工程师们介绍PCB信号完整性设计中常常用到的一些布线技巧,希望能够对各位新人的日常学习和工作带来一定的帮助。

在高速PCB印刷线路板的设计过程中,其基板的印刷电路的成本与层数、基板的表面积是成正比关系的。因此,在不影响系统功能和稳定性的前提下,工程师应该尽可能地用最少层数满足实际设计需要,从而致使布线密度不可避免地增大,而在PCB布线设计中,其走线宽度越细,间隔越小,信号间串扰就越大,其能传送功率越小。因此,走线尺寸的选择必须考虑到各方面的因素。

在PCB的布线设计过程中,工程师需要遵循的原则主要有以下几点:

首先,在布线的过程中设计人员应当尽可能地减少高速电路器件管脚间引线的弯折,采用45度折线,减少高频信号对外的反射和相互间的耦合。

其次,在进行PCB板的布线操作时,设计人员尽可能地缩短高频电路器件管脚间的引线以及管脚间引线的层间交替。高频数字信号走线应尽可能远离模拟电路和控制电路。

除了上面提到的几点PCB布线的注意事项之外,在对待差分信号的问题上,工程师也是需要谨慎处理的。因为差分信号幅度相等且方向相等,所以两条信号线产生的磁场是彼此互相抵消的,因此能有效降低EMI。差分线的间距往往会导致差分阻抗的变化,差分阻抗的不一致将严重影响信号完整性,所以,在实际差分布线时,差分信号的两条信号线相互间长度差必须控制在信号上升沿时间的电气长度的20%以内。如果条件允许,差分走线必须满足背靠背原则,且在同一布线层内。而在差分布线的线间距设置上,工程师需要确保其至少大于等于1倍以上线宽。而差分走线与其他信号线间间距应大于三倍的线宽。

| 我要评论: | |

| 内 容: |

(内容最多500个汉字,1000个字符) |

| 验证码: | 看不清?! |

最新产品

同类文章排行

- 电池电路板未来趋势:探索电池技术的无限可能

- 电路板厂独家分享:电路板PCB相关设计指南(二)

- 5G天线PCB的工艺挑战主要在哪些方面?

- 汽车电路板维修入门指南分享

- 5G线路板:PCB厂如何应对高精度需求

- PCB厂关于线路板制作方法的浅析

- PCB厂:什么是PCB及其特点功能解析

- PCB 特性大揭秘:常用术语深度解读

- 关于汽车无线充电 PCB 的核心技术与设计要点剖析

- 什么是汽车电路板?它与普通电路板有什么不同?

最新资讯文章

您的浏览历史

共有-条评论【我要评论】